資料

ホワイトペーパーとアプリケーションノート

Stress Induced by Silicon-Germanium Integration in Field Effect Transistors

Published in 2015

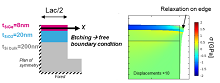

The integration of high level of stress in field effect transistors is performed through incorporation of intrinsically strained SiGe layers. With the help of COMSOL simulations, we performed two studies addressing the level of stress in the area of interest. In the first case, we analyzed the geometric effects of the SiGe film stress relaxation on the edges. In a second time, we studied the final level of stress as a function of different Ge concentrations in both the channel and the source/drain. We found out that the Ge content in the channel has no impact on the stress induced by the source/drain region.

ダウンロード

- berthelon_poster.pdf - 0.34MB

- berthelon_abstract.pdf - 0.04MB