Surface-Trap-Induced Hysteresis in an InAs Nanowire FET — a Density-Gradient Analysis

Application ID: 97361

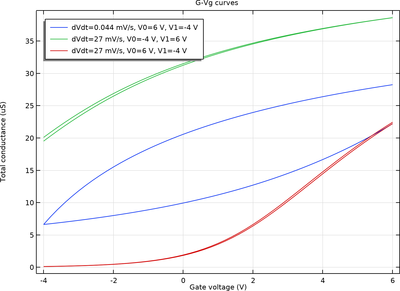

This tutorial analyzes the hysteresis of the conductance-gate-voltage (G-Vg) curves of an InAs nanowire FET, using the density-gradient theory to add the effect of quantum confinement to the conventional drift-diffusion formulation, without a large increase of computational costs. The hysteresis is caused by the dynamic charging effects of fast and slow semiconductor-oxide interface traps of continuous energy distributions and of both donor and acceptor types. The capture probability is modeled as thermally activated with a barrier height that varies with the trap energy level. The qualitative behavior and the order of magnitude of the computed G-Vg curves under various voltage ramping conditions agree well with simulation and experiment results found in the literature.

この model の例は, 通常次の製品を使用して構築されるこのタイプのアプリケーションを示しています.

ただし, これを完全に定義およびモデル化するには, 追加の製品が必要になる場合があります. さらに, この例は, 次の製品の組み合わせのコンポーネントを使用して定義およびモデル化することもできます.

アプリケーションのモデリングに必要な COMSOL® 製品の組み合わせは, 境界条件, 材料特性, フィジックスインターフェース, パーツライブラリなど, いくつかの要因によって異なります. 特定の機能が複数の製品に共通している場合もあります. お客様のモデリングニーズに適した製品の組み合わせを決定するために, 製品仕様一覧 を確認し, 無償のトライアルライセンスをご利用ください. COMSOL セールスおよびサポートチームでは, この件に関するご質問にお答えしています.